前回、ブロック図で設計した回路ブロックの、回路設計に入ります。

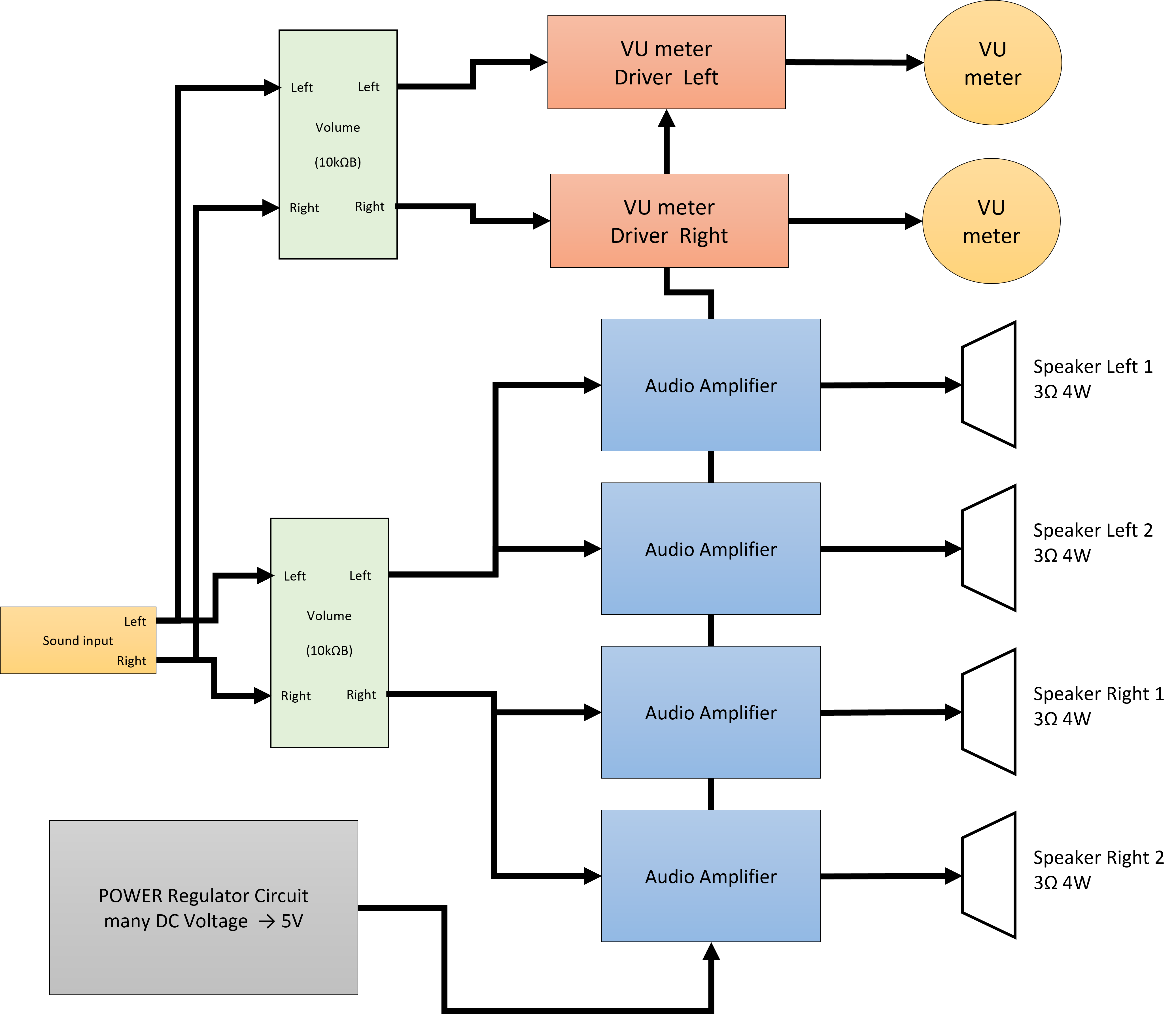

前回示したブロック図を下記に示します。

ここで設計要素がある回路ブロックは、3つ。Audio Amplifier、Power Regulator、VU meter driverの三つです。

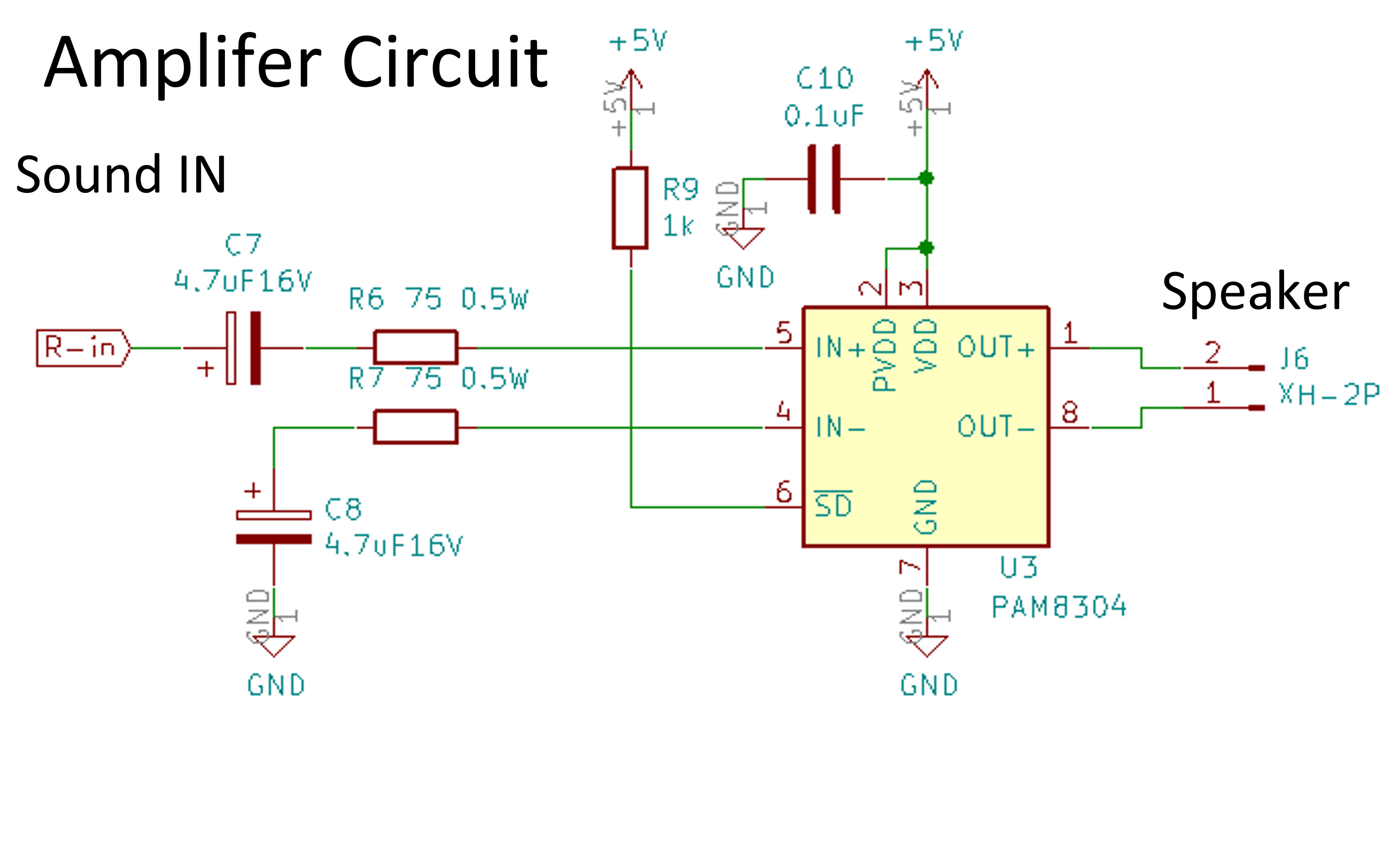

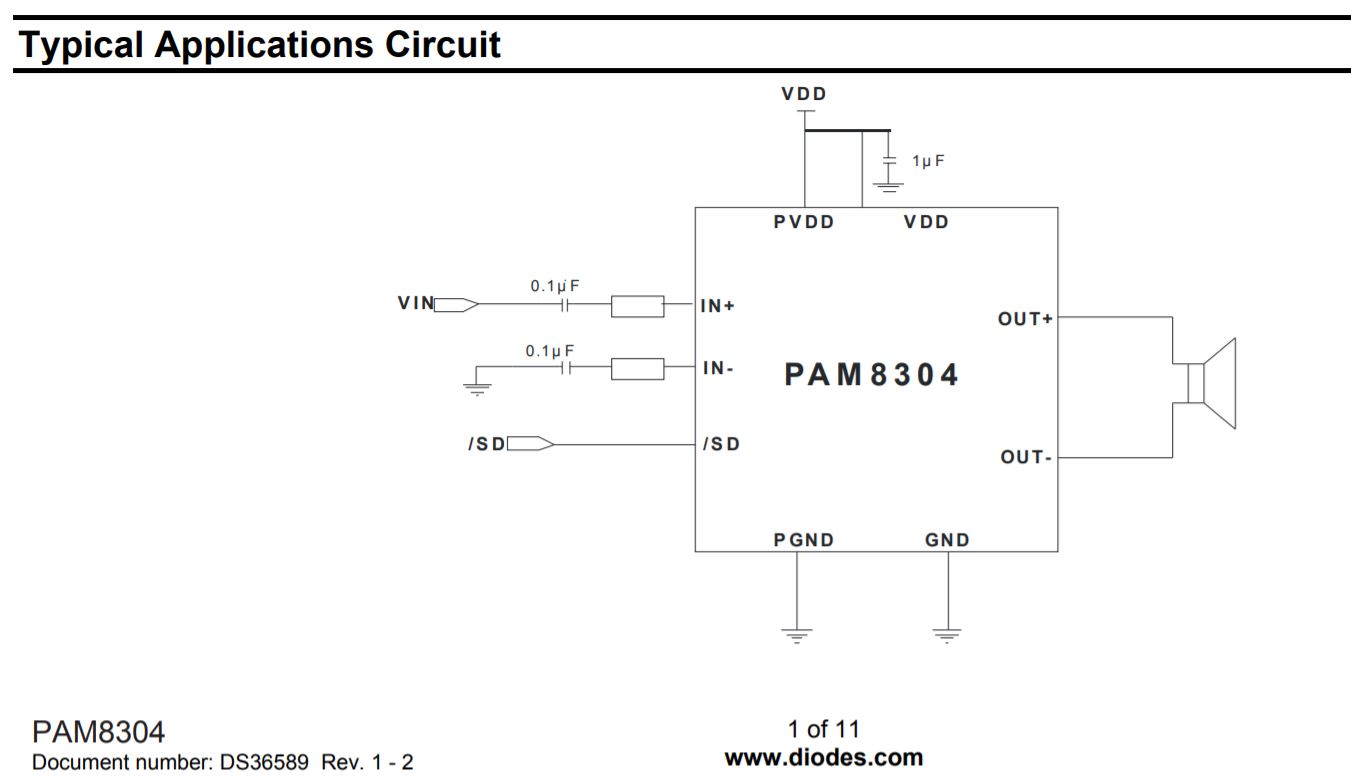

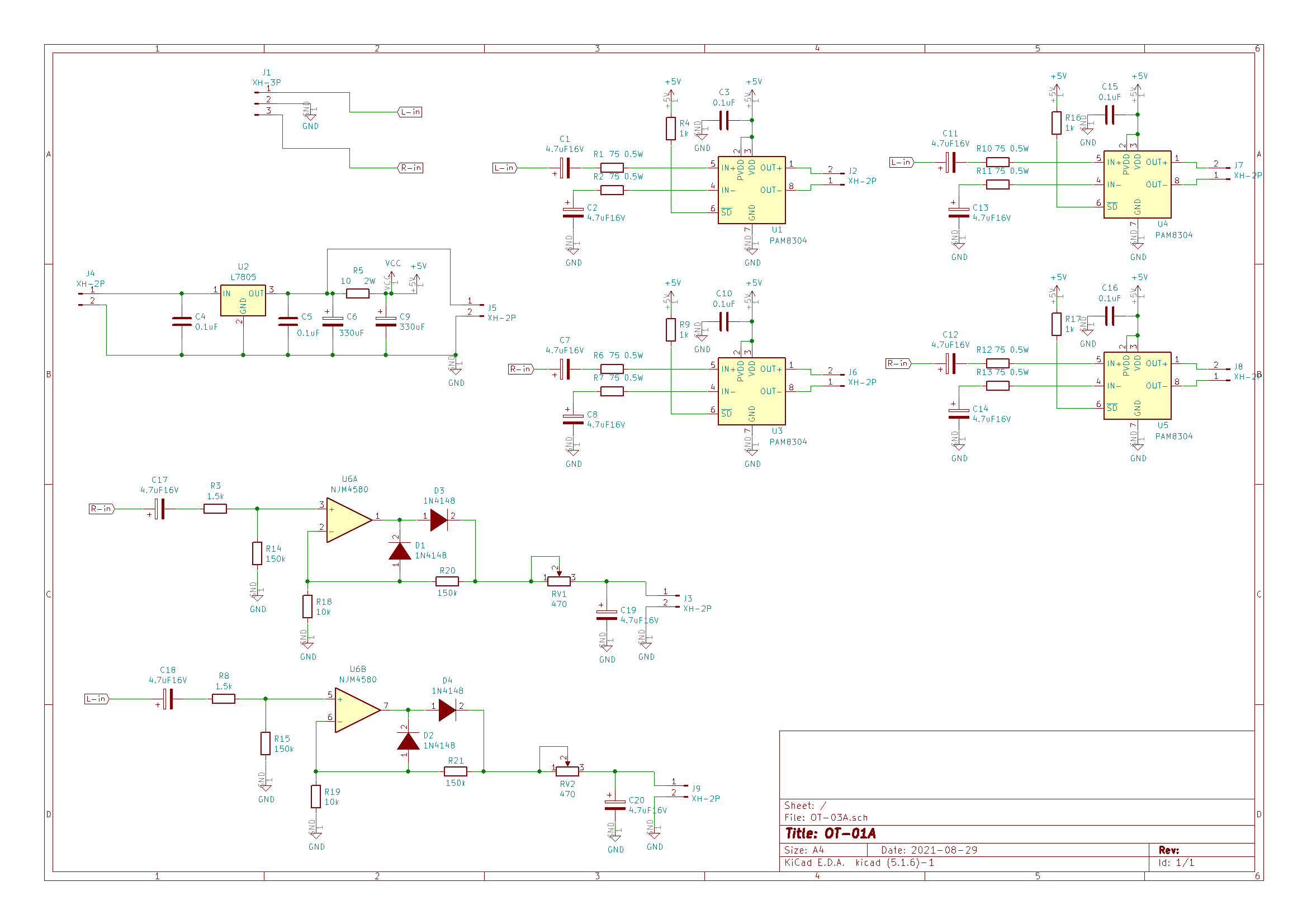

まず、設計したアンプの回路図を示します。

Audio Amplifer(オーディオアンプ回路)

まず、アンプの回路です。

今回は、細かい設計をしなくて済む、アンプ用ICを使いました。

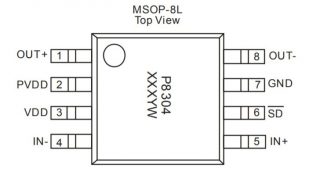

ICは、PAM8304です。

D級パワーアンプIC PAM8304ASR

■主な仕様

・電源電圧:2.8~6V

・出力:

3W typ(5V・4Ω)

1.75W typ(5V・8Ω)

・ゲイン:300000/Rin

(Rin=10kΩなら30倍)

・無信号時消費電流:5mA typ(VDD=5V)

・効率:93% typ(RL=8Ω、THD=10%)

・パッケージ:0.65mm、MSOP8

**秋月電子HPより引用**

回路は、ここのデータシートに記載されている参考回路を使いました。抵抗値やコンデンサは、感覚的に決めました。

SD(シャットダウン)の端子は、プルアップしないと停止してしまうので、プルアップにしています。

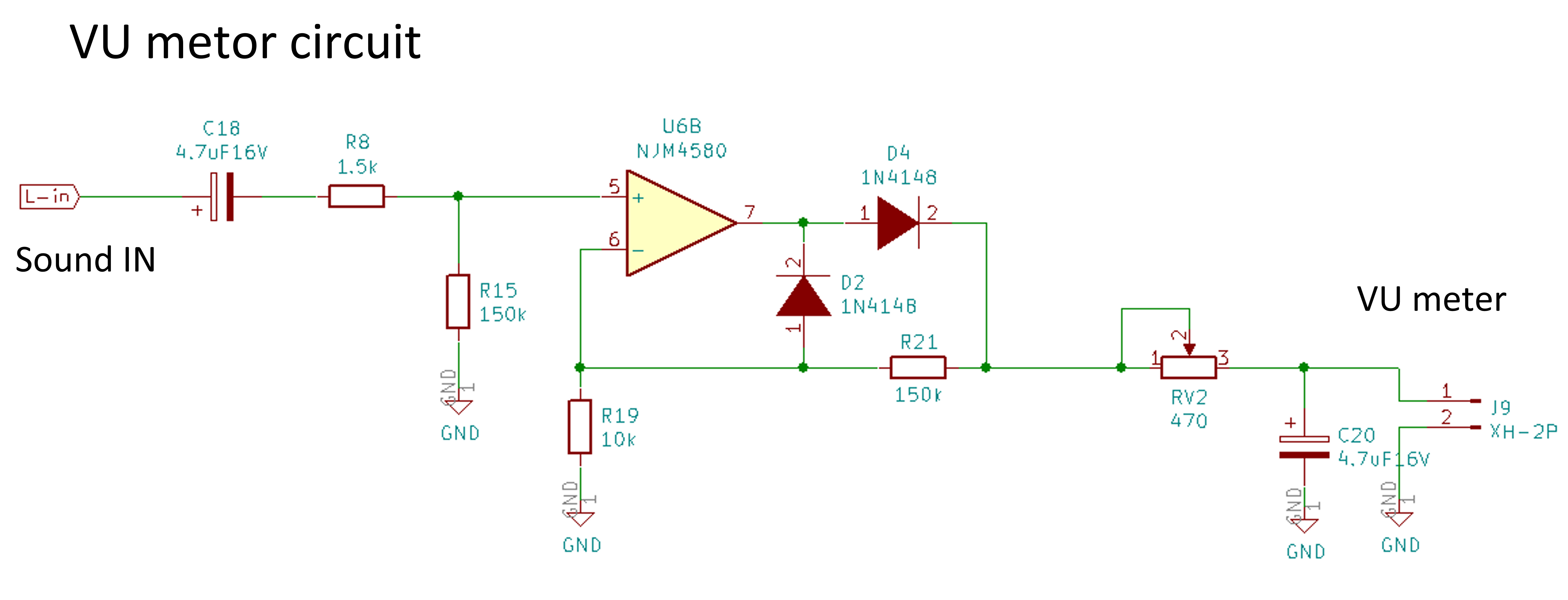

VU meter (VUメータ―回路)

次に、VUメーターの回路です。

VUメータは、いわば直流の電流計です。音声信号を直接入力するのではなく、オペアンプで増幅して、ダイオードで整流(交流から直流に変換する)して、抵抗で電流を調節してVUメータに流します。

オペアンプには、汎用的に使えるNJM4580を使いました。

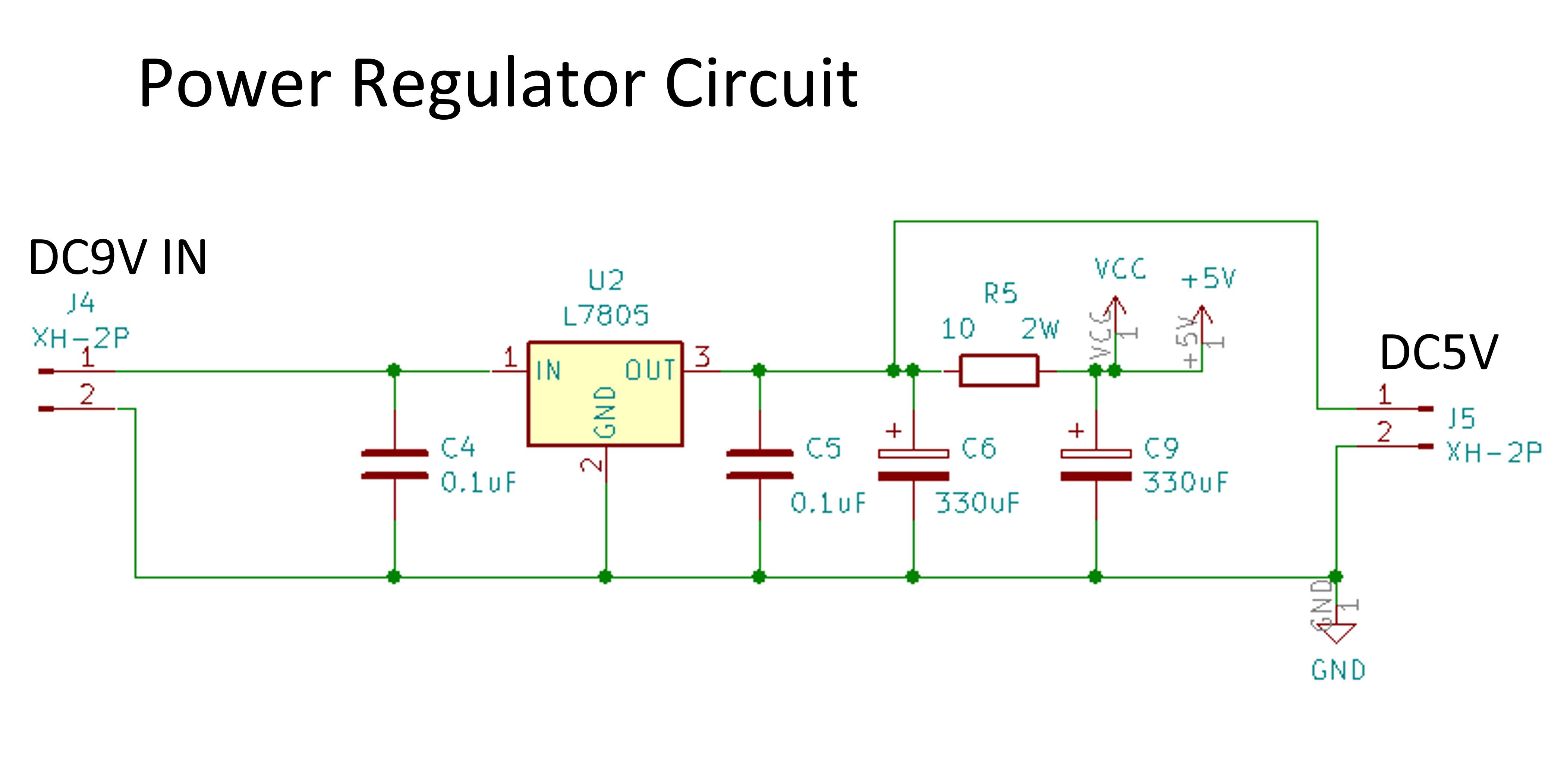

Power Regulator Circuit

次に電源回路です。

アンプICPAM8304の電源電圧が最大6Vなので、5Vの定電圧を流せる回路が必要になります。

回路は3端子レギュレターの一般的な回路です。C4とC5が発振防止のコンデンサ。C6がリップル除去用です。また、R5とC9でRCのローパスフィルタにもなっています。

三端子レギュレーター 5V1.5A TO-252 NJM7805SDL1

■主な仕様

・出力方式:シリーズ

・出力正負:正電源

・入力電圧:~35V

・出力電圧:5V

・最大出力電流:1.5A

・ドロップアウト電圧:2.2V

・許容損失:1190mW

・リップル除去比(PSRR):78dB

・パッケージ:TO-252

**秋月電子より引用**

最後に、全体の回路図を示します。

次回は、この回路の基板設計を行います。